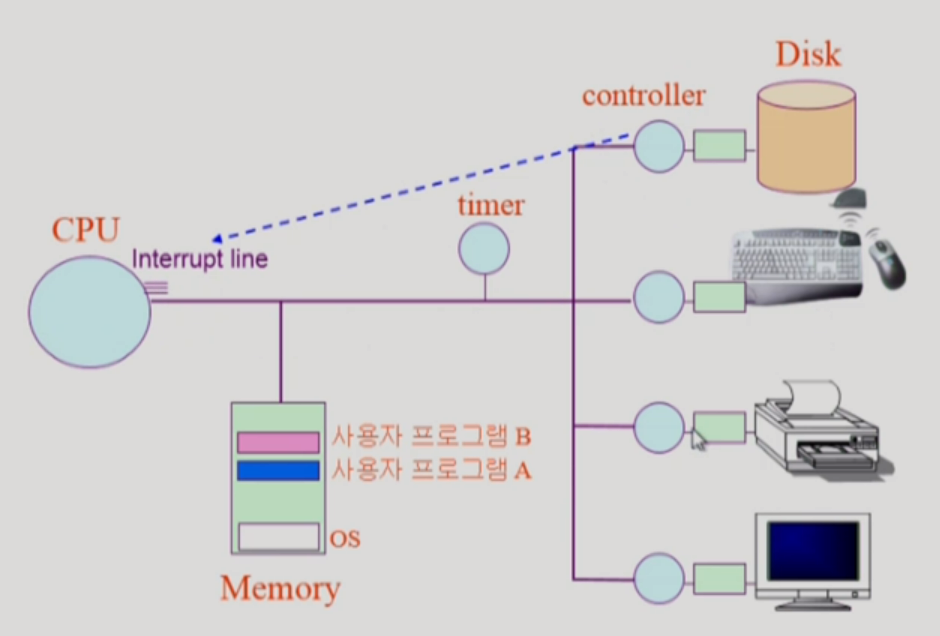

컴퓨터 시스템 구조

1. Memory

CPU의 작업공간.

CPU가 직접 접근할 수 있는 내부 기억장치로, 특정 프로그램이 CPU에서 실행되기 위해서는 해당 부분이 메모리에 올라와 있어야 한다.

컴퓨터 부팅 시, OS는 메모리에 올라가게 됨 -> 메모리에 상주하는 CPU의 작업 공간을 main memory라고 부른다

2. I/O Device

1) Device Controller

- I/O 장치를 관리하는 일종의 작은 CPU로, I/O가 끝났을 경우 interrupt로 CPU에게 해당 사실을 알리는 역할을 한다

- CPU와 I/O device의 처리 속도가 다르기 때문에 device마다 controller를 두어 관리한다.

- 제어 정보를 위해 control register, status register / local buffer(일종의 data register)를 가짐

- 실제 device 와 local buffer 사이에서 I/O가 일어남

cf) device driver : OS 코드 중 각 장치별 처리 루틴(software)

device controller : 각 장치를 통제하는 작은 CPU(hardware)

2) Local Buffer

device controller가 데이터를 임시로 저장하기 위한 작업공간.

buffer에 쌓인 내용을 CPU가 읽어서 자신의 메모리에 복사

3. CPU

- 매 clock cycle마다 register가 가지고 있는 메모리에서 instruction을 읽어서 실행

- interrupt가 들어온 경우, CPU 제어권이 OS에게 넘어간다

- I/O 요청이 발생할 경우 CPU가 아닌 OS -> device controller가 작업을 관장한다.

메인 메모리와 local buffer에 접근할 수 있다.

1) Register

memory보다 더 빠르며 작은 정보를 저장하는 저장 공간

2) Interrupt line

외부 I/O 요청이 들어왔는지 / 작업이 종료되었는지 CPU에게 알려준다.

CPU가 instruction을 수행하던 도중, interrupt line에 신호가 들어오면 해당 interrupt와 관련된 일을 먼저 처리한다.

3) Mode bit

CPU에서 실행되고 있는 프로그램이 운영체제인지 사용자 프로그램인지 구분해준다.

사용자 프로그램의 잘못된 수행으로 다른 프로그램 및 운영체제에 피해가 가지 않도록 하기 위한 보호 장치 필요.

Mode bit을 통해 하드웨어적으로 두 가지 모드의 operation을 지원한다.

- [1] 사용자 모드(=user mode)

- 사용자 프로그램 수행

- 보안 상의 목적으로 제한된 instruction만 수행 가능

- [0] 모니터 모드 (=kernel mode, system mode)

- OS 코드 수행하는 경우로, 모든 일을 수행 가능하다

- interrupt가 발생해서 OS가 CPU를 가지고 있는 경우(OS에서만 I/O device 접근 가능)

- 보안을 해칠 수 있는 중요한 명령어는 모니터(커널, 시스템) 모드에서만 수행 가능한 '특권명령'으로 규정한다.

- Interrupt나 Exception 발생 시 하드웨어가 mode bit을 0으로 바꾼 후 실행해야 한다.

- 사용자 프로그램에게 CPU를 넘기기 전에는 mode bit을 1로 세팅해야 한다.

4. Timer

특정 프로그램이 CPU를 독점하는 것을 막기 위한 장치. Time sharing을 구현하기 위해 이용된다.

- 컴퓨터 시작 : OS가 CPU를 사용자 프로그램에게 넘겨줌(Timer에 값 세팅)

- timer의 값이 0이 되면 timer interrupt 발생

- OS로 다시 CPU 제어권이 넘어옴

5. DMA Controller (Direct Memory Access)

메모리에 직접 접근이 가능한 장치

I/O 장치의 잦은 interrupt로 인한 방해를 막기 위해 local buffer에서 메모리로 데이터를 복사해오는 작업을 CPU 대신 수행

=> CPU에는 1번의 interrupt만 건다!

I/O의 수행

- 모든 입출력 명령은 '특권명령' (OS가 커널모드에서 수행해야 한다 - 독점)

- 사용자 프로그램은 어떻게 I/O를 하는가?

- 시스템콜(System call) : 사용자 프로그램은 운영체제에게 I/O를 요청하기 위해 interrupt를 건다

- monitor bit가 0으로 설정되어 OS에게 CPU가 할당된다

monitor bit가 1인 상태이면 OS의 주소로 점프할 수 없다.

따라서 프로그램이 직접 interrupt line을 세팅하고 CPU에게 interrupt를 보낸다.

CPU는 interrupt가 들어왔기 때문에 mode bit을 0으로 바꾸고 CPU 제어권을 OS로 넘긴다.

(Trap/SW Interrupt를 사용하여 인터럽트 벡터의 특정 위치로 이동)

(제어권이 인터럽트 벡터가 가리키는 인터럽트 서비스 루틴으로 이동) - 올바른 I/O 요청인지 확인 후 I/O 수행

- I/O 완료 시 제어권을 system call 다음 명령으로 옮김

Interrupt

CPU가 프로그램을 실행하고 있을 때, I/O 장치나 예외 상황이 발생해서 처리가 필요한 경우 CPU에게 알리는 이벤트

interrupt가 발생할 때만 CPU 제어권이 OS에게로 넘어간다

- 현대의 운영체제는 인터럽트에 의해 구동됨

Interrupt(넓은 의미)

- Interrupt(하드웨어 인터럽트) : 하드웨어(타이머, disk controller 등)가 발생시킨 인터럽트

- Trap(소프트웨어 인터럽트)

- Exception : 프로그램이 오류를 범한 경우 (ex. memory violation)

- System call : 사용자 프로그램이 OS의 도움을 받기 위해 커널 함수를 호출하는 경우

인터럽트 관련 용어

- 인터럽트 벡터 : 해당 인터럽트의 처리 루틴 주소를 가지고 있음

- 인터럽트 종료 별로 실행해야 할 함수의 주소를 정의해놓음 {번호, 처리해야 할 커널 함수의 주소}

- 인터럽트 처리 루틴(=Interrupt Service Routine, 인터럽트 핸들러) : 해당 인터럽트를 처리하는 커널 함수

- 인터럽트가 실제로 해야 하는 일

- Software interrupt(trap) : I/O 요청

- Hardware interrupt : I/O 종료

System call

사용자 프로그램이 운영체제의 서비스를 받기 위해 커널 함수를 호출하는 것

'💻 CS > 운영체제' 카테고리의 다른 글

| [운영체제] 5. CPU Scheduling (0) | 2022.11.27 |

|---|---|

| [운영체제] 4. Process Management (0) | 2022.11.27 |

| [운영체제] 3. Process (0) | 2022.11.20 |

| [운영체제] 2. System Structure & Program Execution 2 (0) | 2022.11.20 |

| [운영체제] 1. Introduction to Operating Systems (0) | 2022.11.13 |

댓글